# Patterning of silicon layers using a highly selective, single-sided, Gas Phase Process.

<u>, Laurent Clochard <sup>(1)</sup></u>, Paul Tierney <sup>(3)</sup> , Fiacre Rougieux, & Yalun Cai <sup>(4)</sup>, <u>Thorsten Dullweber<sup>(5)</sup></u>, Yevgeniya Larionova<sup>(5)</sup>

1) Nines Photovoltaics,, Dublin, Ireland I.clochard@nines-pv.com

2) Technical University Dublin (TUD), Ireland

4) UNSW, Australia

5) ISFH, Hamelin, Germany

## **Company introduction**

- SME Founded in 2010, Based in Dublin, Ireland

- Innovative, R&D focus, European innovation

- Equipment + process development

- Small , focussed team

- Atmospheric Pressure gas-phase Etching for the PV market

- Financed through Private investments & EU funds

www.innoenergy.com

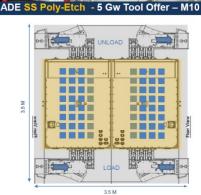

## ADE multi-GW PRODUCTION TOOLS

00

# M10 : 24,000 wph

## ADE-3000 Single Side Etch Series

SS-POLY-ETCH

Dry Etching equipment for High efficiency solar cell

- ADE SS Poly-Etch 24,000 Wfr/hr

- 3 Tools ~5 Gw

- Inline, cassette to cassette; modular configurations

| ADE               |     |

|-------------------|-----|

| SS-POLY-ETCH      | M10 |

| 888 <u>- 8</u> 16 |     |

| ADE-6000-SS Poly-E |                                                   |  |

|--------------------|---------------------------------------------------|--|

| Footprint          | 12 m <sup>2</sup> (6m <sup>2</sup> without loader |  |

| Configuration      | 8 lanes – M10 wafers                              |  |

| Throughput         | 24,000 wafers per hour                            |  |

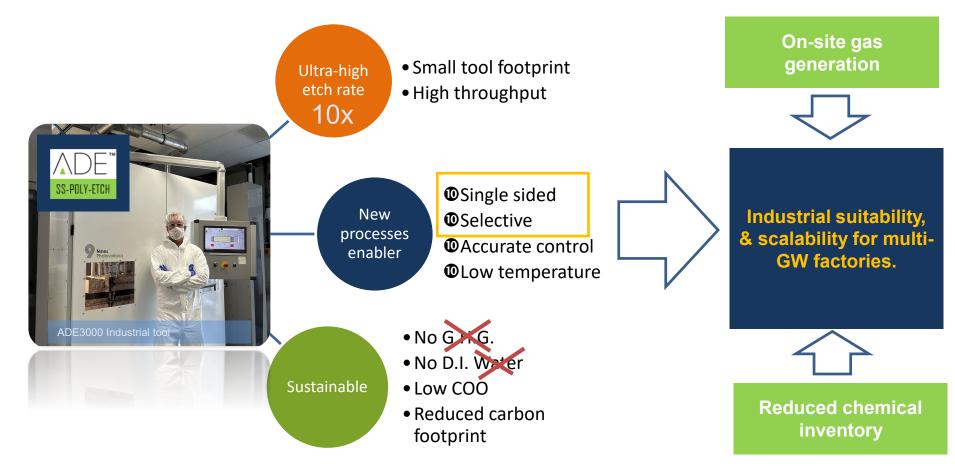

#### **MOTIVATION:** Main Process Advantages of ADE gas-phase etch

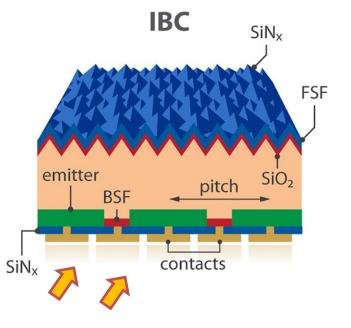

## **Application for BC cells**

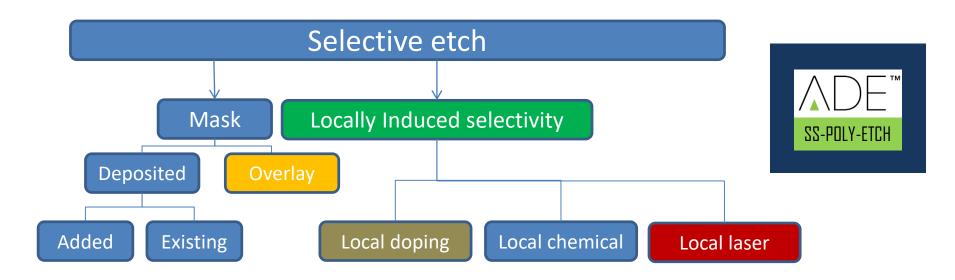

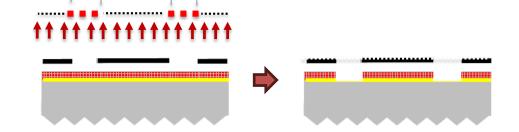

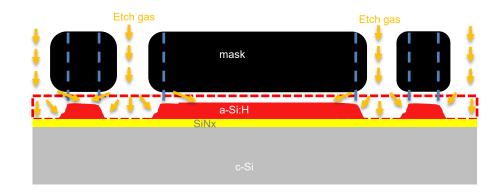

- Next generation cells require patterning

- IBC needs patterning of the rear poly layers

→Need for development of patterning methods

→Exploring Patterning by selective, single side, gasphase etching

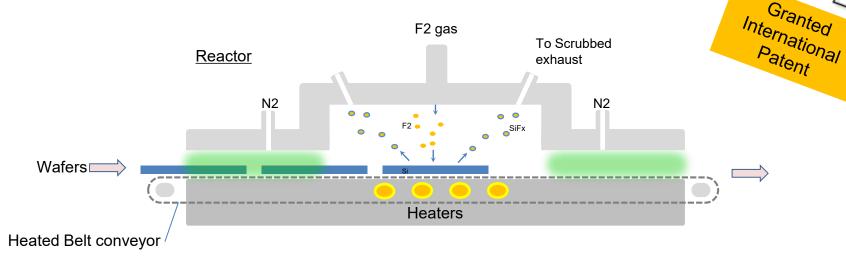

- Thermal process using molecular Fluorine gas (F2)

- Low temperature Chemical etching (NO PLASMA / IONS)

- In-line tool layout with continuous flow of wafers

- Atmospheric pressure process ( no vacuam)

0

**Global Warming Potential**

(100 year GWP kg CO, eq)

F2

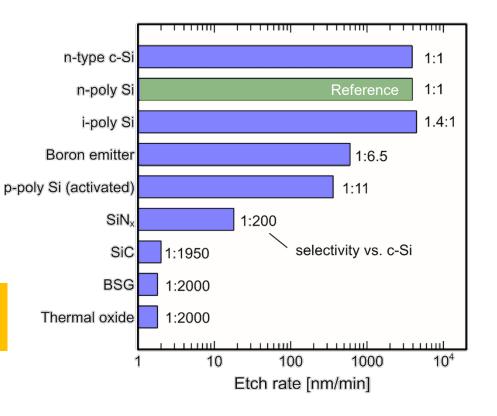

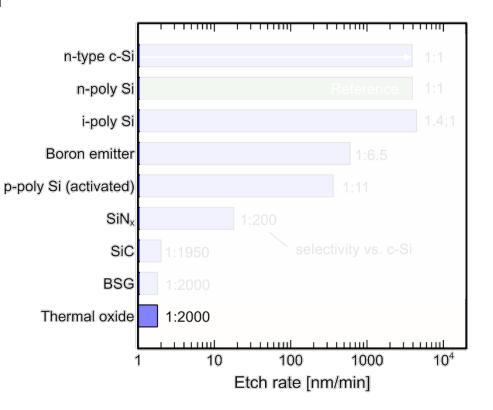

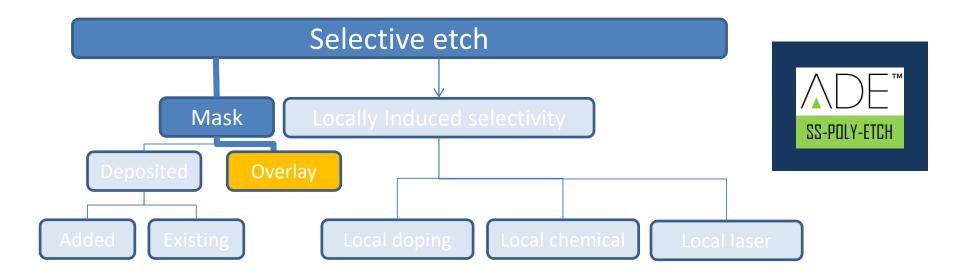

## **Etch selectivity**

- Etch **rate** is the speed of the etching process for a material [nm/min]

- Etch selectivity is the ratio of etch rates between materials

S=E<sub>x</sub>/E<sub>c-Si</sub>

Surface reaction

→ Sensitive to surface state

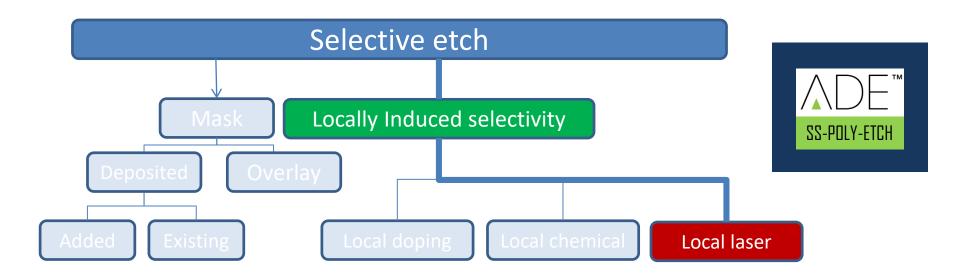

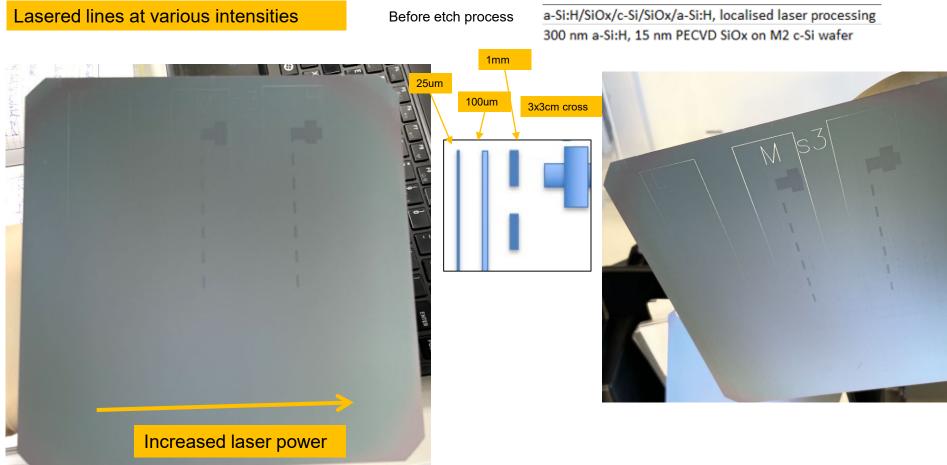

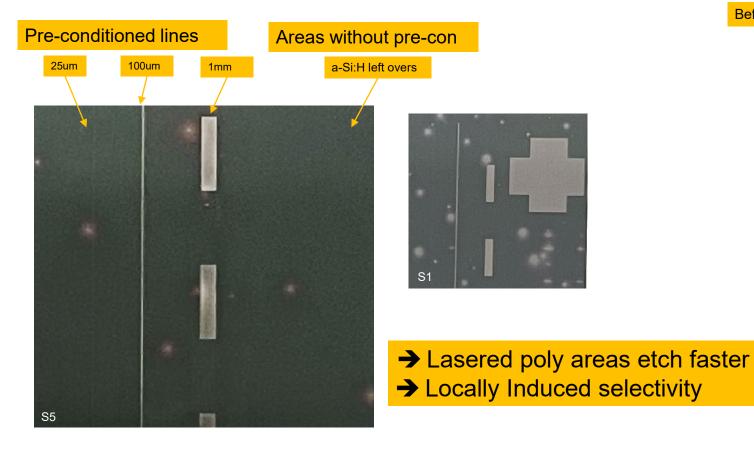

## Localised Laser pre-conditioning

## Localised Laser pre-conditioning

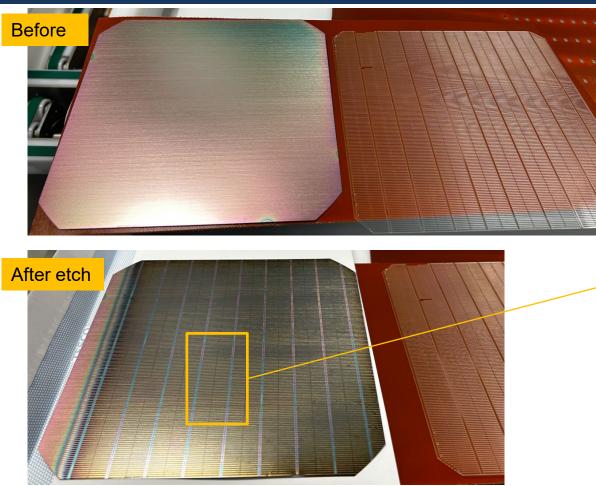

Surface after ADE process of the whole wafer:

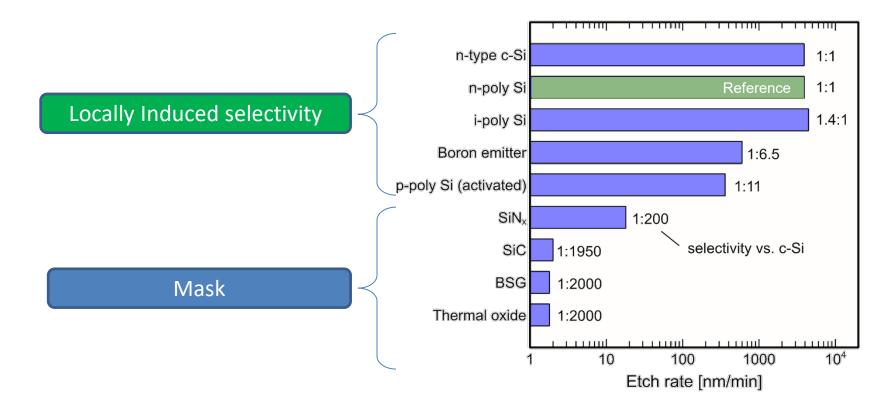

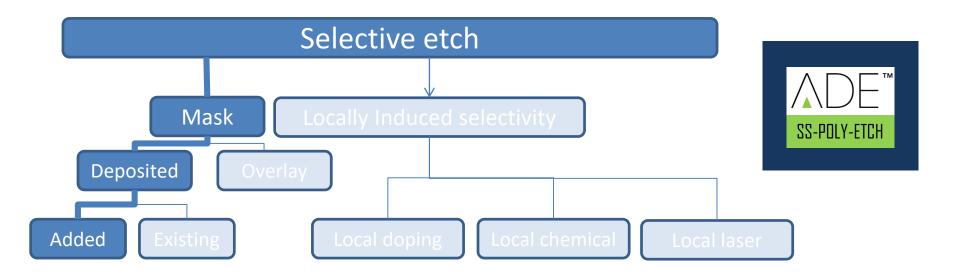

## **1 – Etch selectivity**

- Thermal oxide etch rate 2000 times slower

- More "traditional" mask technic

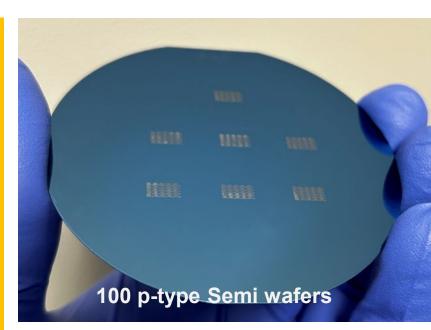

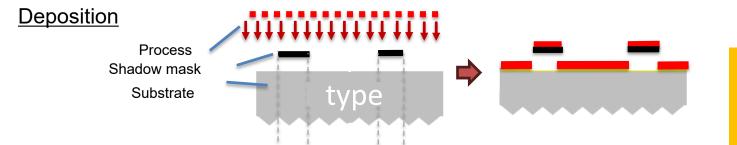

## **Deposited mask – "Semi" process**

#### **OXIDATION:**

Dry oxidised @ 1100 °C → Oxide thickness of circa 120 nm

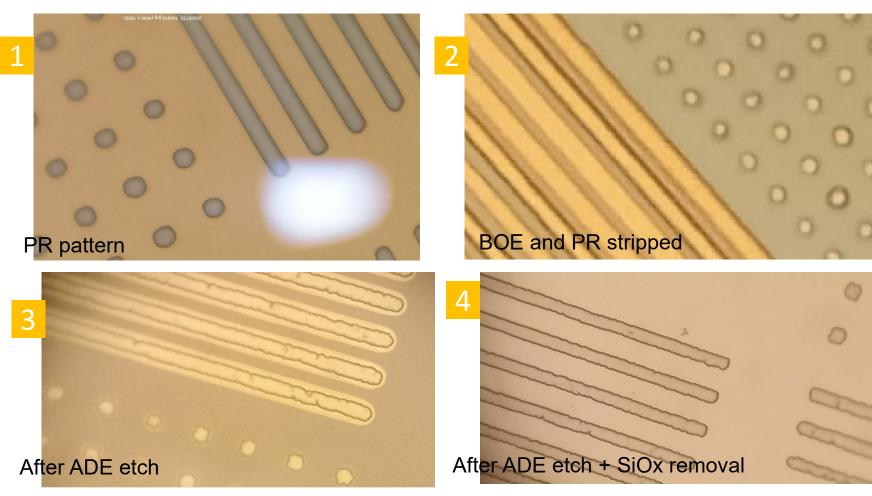

#### **PHOTORESIST:**

- Photoresist (S1818 G2 ) and soft baked @ 115 °C for 60 sec

- Exposed pattern (using a Polos uPrinter)

- Developed pattern (Microsposit 351 developer)

- Hard baked PR @ 135 °C for 180 sec to create etch mask for the SiO2

#### ETCHING

- Etch exposed SiO2 back to the Si surface (10:1 BOE for 120 sec)

- Photoresist strip (Microposit SVC175 PR stripper)

- ADE Gas-Phase etch of the exposed silicon

- Remove remaining SiO2 (HF etch)

## 4/6 samples

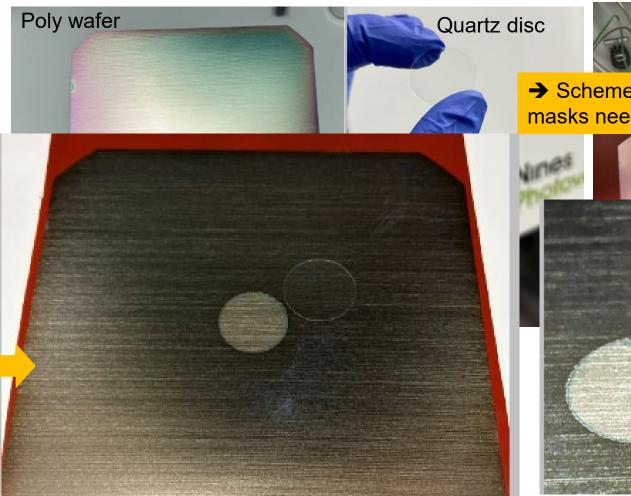

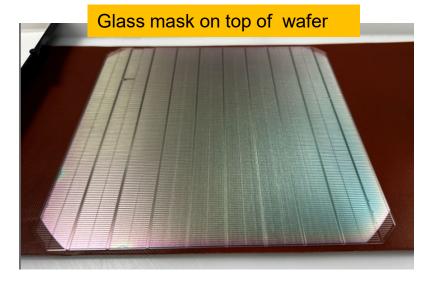

→ Schemes with more elaborated shadow masks need to be explored

- M2 wafer

- 80nm SiNx + 150nm a-Si:H

- ➔ Allows easy visual inspection

Negative version

Selective etching of poly layer

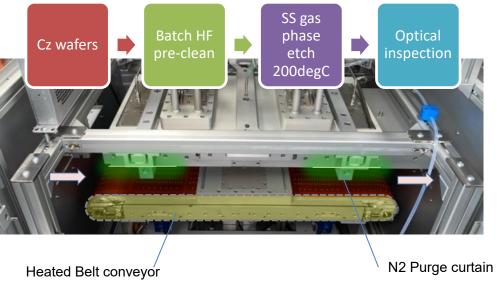

## **Experimental**

- Cz wafers pre-cleaned in 5%HF solution

- Wafers are etched in an inline gas-phase etch tool (ADE100) at around 200 DegC

- <20s process time</li>

Results

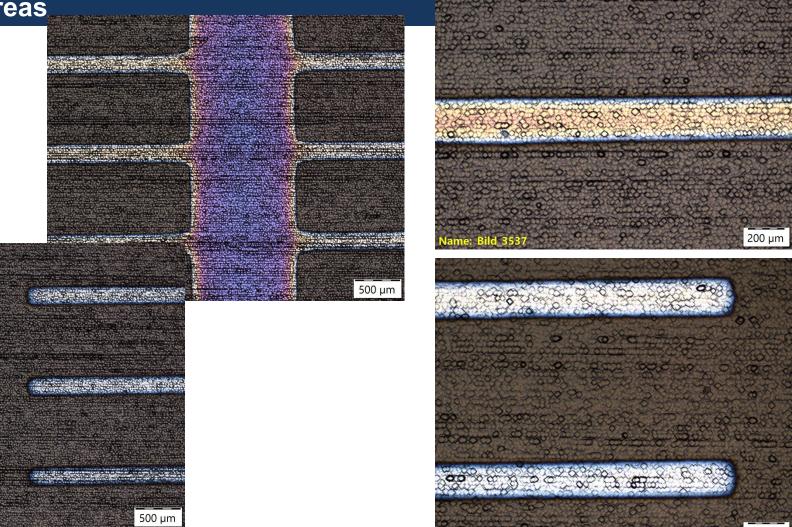

## The better areas

Name: Bild\_3544

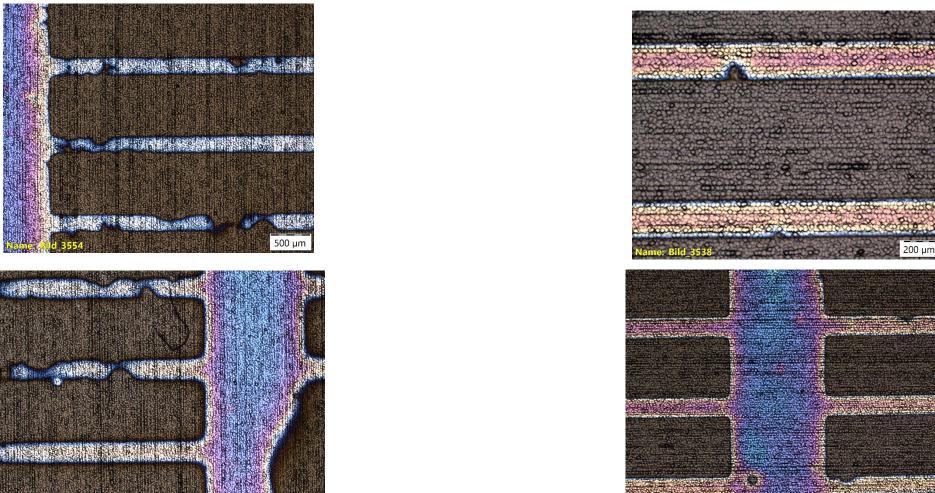

### Some defect area

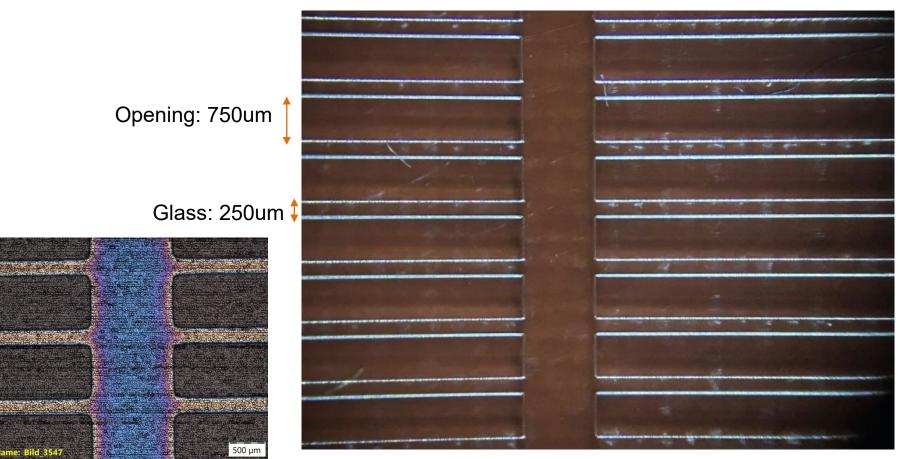

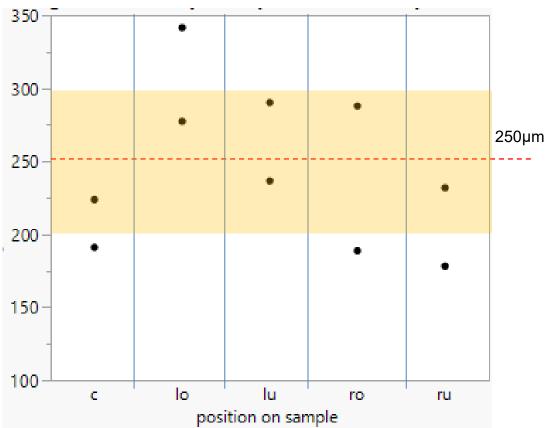

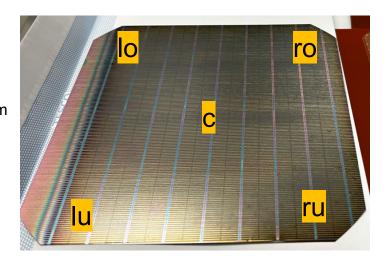

## **Finger width variations**

Measured finger width (um)

Position on sample

→ Large enough relative variation

- Fine process tuning

- Understanding of "reach"

- Optimization of mask & uniformity

- Trials without etch stop under-layer

## Take away :

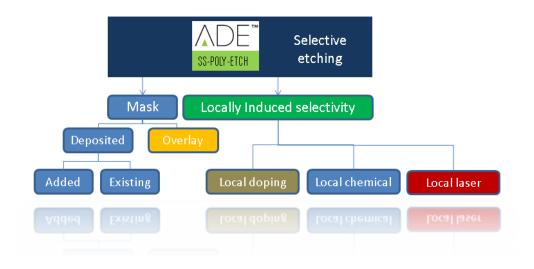

- High selectivity of ADE single-side gas-phase etch

- Enables several paths and **options for patterning** poly-silicon layers

- → masking

- → Locally induced selectivity

- Let's take advantage of it !

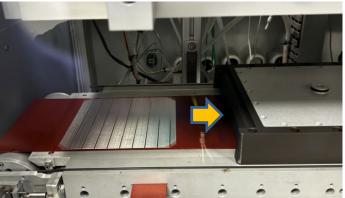

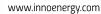

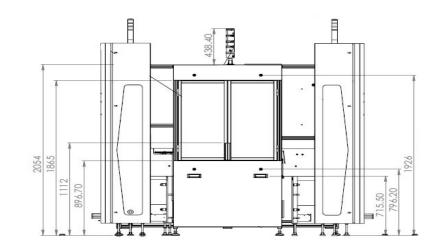

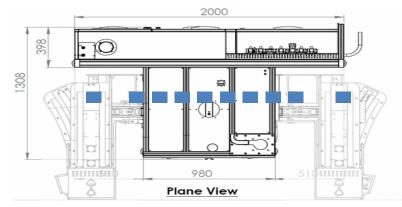

#### ADE100 – R&D Pilot line

Shown with loaders